An FPGA is used to implement a digital system, but a simple microcontroller can often achieve the same effect. Microcontrollers are inexpensive and easy to drop down on a PCB. FPGAs are powerful tools, but may not be a good fit for every case.

They have more power, layout, and external circuit requirements that can be prohibitive. Using an FPGA that is considerably more expensive and has lots of special requirements might seem like a ludicrous notion.

You may have already guessed the first reason you might need an FPGA: flexibility. Having configurable logic blocks means you’re never stuck with your hardware. You can never run out of timers or UARTs as long as you have logic elements available to create another one. Being able to reconfigure down the road can also extend the life cycle of a product as technology and requirements change.

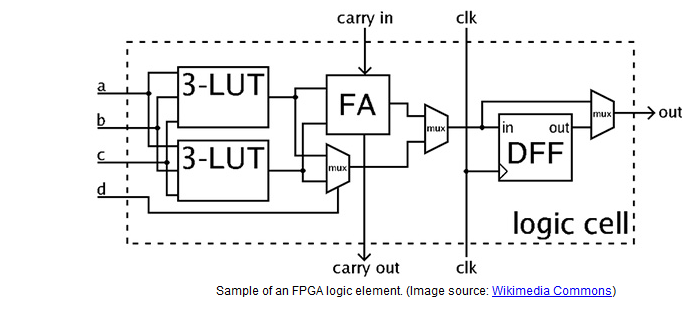

The second reason is speed. A microcontroller executes instructions one at a time, sequentially. An FPGA structure is inherently parallel because of its hardware nature. This allows things to occur simultaneously which is useful for operations like the FFT or graphics processing which can be expensive on a sequential processor. FPGAs also have more high-speed I/O options than a typical microcontroller like LVDS and transceivers capable of 10+ Gbps for protocols like HDMI.

What is FPGA programming?

FPGAs use a special type of language called HDL, or Hardware Description Language. There are two primary flavors: Verilog and VHDL. Nearly every development suite like Quartus or Vivado will support both so which you decide to use is a matter of preference. These languages are then “synthesized”, which is analogous to compilation for microcontrollers. The synthesis tool tells the FPGA how to connect its logic elements to create the effect described by your code. Remembering that your code is being translated into hardware and not CPU instructions is important to remember when you’re first getting started.

To make development easier, FPGA vendors supply you with a catalog of commonly used code blocks that can be easily dropped into a design. These include things like multipliers, RAM, communication blocks, and more. They can be configured and added into your design without ever having to look at the HDL code involved, speeding up your development time.

FPGA programming or FPGA development process is the process of planning, designing and implementing a solution on FPGA. The amount and type of planning vary from application to application. But creating a requirements document that captures all specific requirements and creating a design document that explains how the proposed solution would be implemented can be very helpful to enumerate potential problems and plan around them. A little bit of time spent creating a quality design document will save tons of time in refactoring, debugging and bug fixing later.

Implementing a solution on FPGA includes building the design using one of the design entry methods such as schematics or HDL code such as Verilog or VHDL, Synthesizing the design (Synthesis, netlist generation, place and route etc..) in to output files that FPGAs can understand and program the output file to the physical FPGA device using programming tools.

RTL- RTL stands for Register Transfer Level. You might also encounter the terms Register Transfer Logic or Register Transfer Language, they all mean the same in the context of hardware designing. RTL is a higher level abstraction for your digital hardware design and comes somewhere between strictly behavioral modeling on one end and purely gate-level structural modeling on other ends. Behavioral modeling is explained in the next articles in this series so don’t be daunted with this term. Gate modeling means describing hardware using basic gates which is quite tedious. RTL can also be thought of as analogous to the term “pseudo-code” used in software programming. It is possible to describe the hardware design as sequences of steps (or flow) of data from one set of registers to next at each clock cycle. Therefore, RTL is also commonly referred to as “dataflow” design. Once the RTL design is ready, it is easier to convert it into actual HDL code using languages such as Verilog, VHDL, SystemVerilog or any other hardware description language. HDL and Verilog are explained in the next section. Check out the Wikipedia page on RTL for more information (https://en.wikipedia.org/wiki/Register-transfer_level)

Verilog

In the previous paragraphs, I mentioned the word “oversimplified” two times. The reason is that FPGAs are much much more than just a bunch of gates. While it is possible to build logic circuits of any complexity simply by arranging and connecting logic gates, it is just not practical and efficient. So we need a way to express the logic in some easy to use format that can be converted to an array of gates eventually. Two popular ways to accomplish this are schematic entry and HDLs (Hardware Description Language).

Before HDLs were popular, engineers used to design everything with schematics. Schematics are wonderfully easy for small designs but are painfully unmanageable for a large design (think about Intel engineers drawing schematics for Pentium, which has millions of gates! it is unacceptably complex). If you have some electronics background, your initial tendency will be to use schematics to realize your design instead of learning a new language (This happened to me, honestly). For the aforementioned reasons, we will stick with HDL throughout this tutorial.

Verilog is a Hardware Description Language (HDL) which can be used to describe digital circuits in a textual manner. We will write our design for FPGA using Verilog (as if you write microcontroller programs in C and Assembly). Learning Verilog is not that hard if you have some programming background. VHDL is also another popular HDL used in the industry extensively.

Verilog and VHDL share more or less same market popularity, but I chose Verilog since it is easy to learn and its syntactical similarity to C language. Once you are comfortable with Verilog, it should be easy learning VHDL as well. Want to read more about Verilog? Check out this wiki page (http://en.wikipedia.org/wiki/Verilog) or check this tutorial (http://www.asic-world.com/verilog/index.html).

Some vendors also have High Level Synthesis (HLS) tools that can translate a function written in C or C++ into a block of HDL code. Using these tools greatly reduces the barrier to entry for developers with a software background by abstracting away some of the low-level details.

Tagged: FPGA, FPGA programming, HDMI, LVDS, microcontroller, UART

An FPGA is used to implement a digital system, but a simple microcontroller can often achieve the same effect. Microcontrollers are inexpensive and ea

[See the full post at: What is FPGA programming? ]

What is FPGA programming?

Related posts:

Related posts: