An automatic instruction set refers to a set of instructions that are executed automatically by a program or a device without the need for human intervention.

In computer science, an instruction set is a collection of commands and operations that a processor can execute. An automatic instruction set, therefore, would consist of a predefined sequence of these commands that are executed in a specific order without the need for human input.

Examples of automatic instruction sets can be found in various fields, such as robotics, where pre-programmed instructions can direct a robot’s actions without the need for human control. Automatic instruction sets can also be used in software applications, such as macros, which automate repetitive tasks in a program.

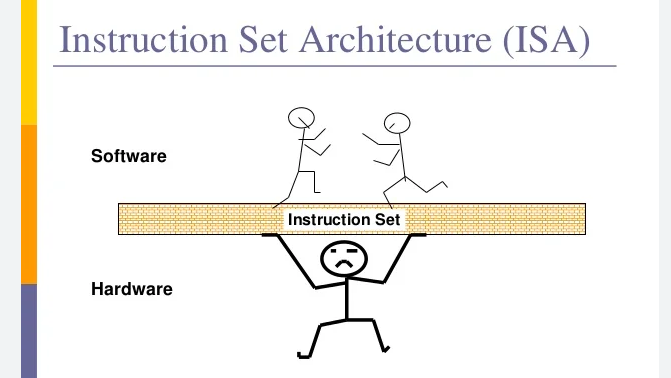

The Instruction Set Architecture (ISA) is the part of a computer architecture that is related to programming. It serves as the interface between software and hardware. The ISA defines the supported instructions, data types, registers, addressing modes, memory architecture, interrupt and exception handling, and external I/O.

Components of ISA

- Instructions: The set of operations that the processor can execute, such as arithmetic operations (add, subtract), data movement (load, store), control flow operations (jump, branch), and special instructions.

- Data Types: Defines the types of data that the processor can handle, such as integers, floating-point numbers, characters, and sometimes more complex types.

- Registers: Small, fast storage locations directly within the CPU used to hold data that is being processed. The ISA defines the number, size, and purpose of these registers.

- Addressing Modes: The ways in which the processor can access data stored in memory. Common addressing modes include immediate, direct, indirect, register, and indexed.

- Memory Architecture: Defines how memory is organized and accessed, including concepts like byte ordering (endianness), memory alignment, and address space.

- Interrupt and Exception Handling: The mechanisms for handling asynchronous events (interrupts) and errors (exceptions), ensuring that the processor can respond to different types of signals and continue processing.

- External I/O: Methods for the processor to communicate with external devices, such as keyboards, displays, and storage devices.

Importance of ISA

- Software Compatibility: An ISA ensures that software written for a specific architecture can run on any processor that implements that ISA, providing a stable platform for software development.

- Hardware Design: The ISA provides a clear specification for hardware designers, outlining the functionality that the processor must support. This helps in creating compatible and efficient hardware.

- Performance Optimization: Understanding the ISA allows software developers to write programs that make efficient use of the processor’s capabilities, leading to better performance.

- Portability: By adhering to a specific ISA, software can be more easily ported to different systems that use the same ISA, reducing the need for extensive rewriting or optimization.

- Standardization: An ISA standardizes the way instructions are executed, making it easier for developers to predict how their code will perform on different hardware implementations.

- Development Tools: ISAs enable the creation of development tools such as compilers, assemblers, and debuggers, which rely on the defined instruction set to translate high-level code into machine code.

Types of Instruction Set Architecture

There are several types of Instruction Set Architectures (ISAs), each with its own design philosophies and characteristics. The most common types are:

1. Complex Instruction Set Computer (CISC)

- Definition: CISC architectures are designed to execute complex instructions that can perform multiple operations in a single instruction. The idea is to reduce the number of instructions per program, sacrificing the number of cycles per instruction.

- Characteristics:

- Instructions can vary in length.

- Rich set of instructions, including many specialized ones.

- More addressing modes.

- Complex decoding logic.

- Examples: x86, VAX.

2. Reduced Instruction Set Computer (RISC)

- Definition: RISC architectures focus on a small, highly optimized set of instructions that are all of uniform length. The idea is to increase the instruction throughput by simplifying the instructions and enabling faster execution.

- Characteristics:

- Fixed instruction length.

- Load/store architecture (only load and store instructions access memory).

- Simple addressing modes.

- Simple decoding logic.

- Examples: ARM, MIPS, SPARC, RISC-V.

3. Very Long Instruction Word (VLIW)

- Definition: VLIW architectures are designed to exploit instruction-level parallelism by encoding multiple operations into a single, long instruction word. The compiler is responsible for identifying parallelism.

- Characteristics:

- Long instruction words containing multiple operations.

- Requires advanced compiler technology to schedule instructions.

- Simple hardware design since parallelism is managed by the compiler.

- Examples: Intel Itanium, TI TMS320C6x.

4. Explicitly Parallel Instruction Computing (EPIC)

- Definition: EPIC is similar to VLIW but includes additional features to exploit parallelism and instruction-level execution more explicitly.

- Characteristics:

- Combines features of VLIW and RISC.

- Utilizes bundles of instructions with explicit parallelism.

- Includes predicated execution and speculation to enhance performance.

- Example: Intel Itanium (Itanium is often considered both VLIW and EPIC).

5. Minimal Instruction Set Computer (MISC)

- Definition: MISC architectures use a very small set of instructions, often for simplicity and minimalism.

- Characteristics:

- Extremely small set of instructions.

- Simplified hardware design.

- Often used in educational contexts or highly specialized applications.

- Example: Forth processors.

6. Stack-Based Architecture

- Definition: Stack-based architectures use a stack to hold intermediate values and operate on top-of-stack elements.

- Characteristics:

- Instructions implicitly operate on the stack.

- Simple instruction set.

- Examples: Java Virtual Machine (JVM), Forth.

7. Accumulator-Based Architecture

- Definition: Accumulator-based architectures use a single accumulator register for arithmetic and logic operations.

- Characteristics:

- Instructions operate on the accumulator and memory.

- Simple design, but limited flexibility.

- Example: Early computers like the PDP-8.

8. Register-Memory and Memory-Memory Architectures

- Register-Memory:

- Instructions can operate on both registers and memory.

- Example: x86 (partly).

- Memory-Memory:

- Instructions operate directly on memory operands.

- Example: Early IBM System/360.

Examples of ISAs

- x86: Widely used in desktop and server processors, known for its complex and variable-length instructions.

- ARM: Common in mobile devices and embedded systems, known for its efficiency and simplicity.

- MIPS: Used in various embedded systems and academic contexts, known for its straightforward and clean design.

- RISC-V: An open-source ISA that is gaining popularity for its flexibility and potential for customization.